新書推薦:

《

帝国的叙事话语:国家身份塑造与冷战时期美国外交政策 北京大学人文学科文库

》

售價:HK$

151.8

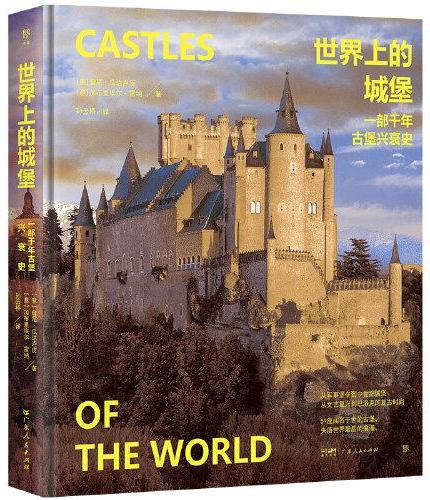

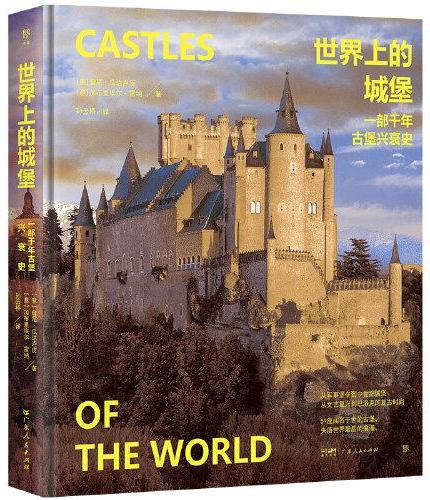

《

世界上的城堡:一部千年古堡兴衰史(从军事建筑到中世纪城堡,59座经典古堡,高清全彩图文,精装收藏品质)

》

售價:HK$

261.8

《

缪斯的诞生 现代西方艺术观念生成简史

》

售價:HK$

85.8

《

信念危机:投资者心理与金融脆弱性

》

售價:HK$

74.8

《

喵星语解密手册

》

售價:HK$

86.9

《

新型戏剧编剧技巧初探

》

售價:HK$

82.5

《

历代玉器收藏与鉴赏

》

售價:HK$

396.0

《

铁腕拗相王安石:北宋的改革家和变法者

》

售價:HK$

107.8

|

| 目錄:

|

Contents

Preface

1 Introduction to NoC 1

1.1 Development of Computer Architecture 1

1.2 Chip Multiprocessor 3

1.3 On-chip Structure and NoC 6

1.4 Summary 10

2 Hybrid Network and Bus On-Chip Interconnection 11

2.1 Introduction 11

2.2 Hybrid On-chip Interconnection with NoC and the Bus 13

2.2.1 Motivation 13

2.2.2 On-Chip Structure 14

2.2.3 Support for Thread Scheduling 15

2.2.4 Experiments and Results 16

2.3 Dynamic Configurable On-Qiip Network with the Hybrid Bus and Networks 18

2.3.1 Motivation 18

2.3.2 BusNoC Hybrid Interconnection 19

2.3.3 Component Design 21

2.3.4 Experiment and Results 23

2.4 Summary 28

3 On-Chip Structure and Optimizations 30

3.1 Introduction 30

3.2 Dynamic Reconfigurable Networks for IO-Supported Parallel Applications 31

3.2.1 Background 31

3.2.2 Architecture Design 33

3.2.3 Implementation 37

3.2.4 Experiments and Analysis 42

3.3 Critical Path-Driven Routers for the On-Chip Network 46

3.3.1 Background 46

3.3.2 Motivation 48

3.3.3 Architecture 51

3.3.4 Implementation 53

3.3.5 Experiments and Analysis 56

3.4 Transmission Bypass Optimization for On-Chip Cores 60

3.4.1 Background 60

3.4.2 Motivation 61

3.4.3 Design 62

3.4.4 Implementation 65

3.4.5 Experiments and Analysis 68

3.5 Summary 75

4 On-Chip Networked Memory System for NoC 77

4.1 Introduction 77

4.2 Network Main Memory Architecture for NoC 78

4.2.1 Background 78

4.2.2 Motivation 80

4.2.3 Basic NMM Architecture 81

4.2.4 Management of NMM and Software Model 85

4.2.5 Experiments and Analysis 87

4.3 Distributed Memory Management Units Architecture for NoC 94

4.3.1 Background 94

4.3.2 Motivation 98

4.3.3 Architecture Model 100

4.3.4 Experiments and Analysis 104

4.4 Summary 108

5 Efficient Task Mapping Algorithm with Low-Power Design for NoC 110

5.1 Introduction 110

5.2 Efficient Task Mapping Algorithm with Power-Aware Optimization for NoC 111

5.2.1 Background Ill

5.2.2 Motivation 112

5.2.3 System Model 114

5.2.4 Proposed Algorithm Design 119

5.2.5 Experiments and Analysis 129

5.3 Energy-Efficient Design of the Microkernel-Based On-Chip OS for NoC 133

5.3.1 Background 133

5.3.2 Motivation 134

5.3.3 Design Overview 136

5.3.4 Distributed On-Chip Operating System 139

5.3.5 Experimental Results and Analysis 144

5.4 Summary 151

6 Conclusions 153

References 156

|

|